# Three-Dimensional X-Ray Laminography as a Tool for Detection and Characterization of BGA Package Defects

Thomas D. Moore, Senior Member, IEEE, Daniel Vanderstraeten, and Pia M. Forssell

Abstract—Non-destructive examination of the layers of a built-up substrate was achieved using three-dimensional (3-D) x-ray microlaminography, with successful separation of layers as thin as 8  $\mu$ m. The same technology was used to create reconstructed images of both surface and internal details of inner solder balls in a ball grid array package soldered to a printed circuit board. Microlaminography was also used to identify bond-wire shorts in the plane of the solder resist of a ball grid array assembly, and these were subsequently verified by destructive physical analysis. This plane is  $\bar{20} \mu m$  thick and immediately adjoining a plane of copper traces; the success demonstrates the capability of microlaminography to resolve and separate very fine detail internally within IC structures. The limits of capability of this machine were also determined; it was found that a crack of approximately 5  $\mu$ m wide in a copper trace of a BGA was not detected by the machine.

As an introduction, the technology and methodology of 3-D x-ray microlaminography are explained. The results from a microlaminography system adapted for failure analysis in integrated circuit packaging are presented. It is shown that such results could not be extracted by two-dimensional (2-D) x-ray or other nondestructive methods.

*Index Terms*—Ball grid array, failure analysis, nondestructive, reconstruction, tomography, 2-D, x-ray.

# I. BACKGROUND

## A. Introduction

THE internal structure of a conventional leaded package is quite simple, and the materials used have distinctly different levels of absorbency of x-rays. Thus the presence and the location of internal defects in this type of integrated circuit (IC) package may be determined readily by conventional two-dimensional (2-D) x-ray. Furthermore, the attachment of these packages to the printed circuit board (PCB) is by means of externally disposed leads; these are amenable to visual inspection.

By comparison the structure of a ball grid array (BGA) package is complex, especially where there are more than two

Manuscript received June 1 2001; revised February 4, 2002. This paper was presented in part at the 8th International Physics and Failure Analysisis Symposium, Singapore, July 10–13, 2001. This work was supported under the EXCEL project sponsored by EU with funding under the Information Society Technologies program. This work was recommended for publication by Associate Editor C. Ume upon evaluation of the reviewers' comments.

- T. D. Moore is with Analog Devices BV, Limerick, Ireland (e-mail: tom-d.moore@analog.com).

- D. Vanderstraeten is with the Alcatel Microelectronics, Oudenaarde, Belgium (e-mail: Daniel.vanderstraaeten@alcatel.com).

- P. M. Forssell is with Nokia Mobile Phones, Ltd., Salo, Finland (e-mail: pia.forssell@nokia.com).

Publisher Item Identifier S 1521-3331(02)03532-8.

copper layers in the substrate, or where the assembly contains several ICs or other components. Lead in solder has a high attenuation of x-rays. Thus the solder balls block out details of other parts of the package in x-ray images. In addition their position as an array on the underside of the package requires the use of x-ray or other penetrating radiation for their inspection.

A variety of failure analysis techniques for BGA was presented in [1], including acoustic microscopy, parallel polishing and focussed ion beam (FIB) examination. Only the first of these is nondestructive, but internal defects must be large to be detected. Other destructive techniques have been developed to enable fine defects in individual BGA substrate layers to be identified and examined [2]. For such fine defects an alternative non-destructive technique to acoustic microscopy is needed.

# B. X-Ray Laminography

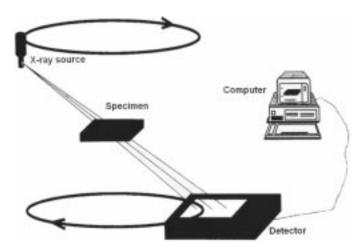

X-ray laminography is a nondestructive radiographic process for capturing three-dimensional (3-D) information about the internal structure of an object. It is related to x-ray tomography (commonly known as CAT-scan). In tomography the object is rotated on an axis perpendicular to the x-ray beam, and data is gathered about slices perpendicular to the axis of rotation. In laminography the object is moved in a small diameter orbital path around the center of an inclined x-ray beam. In many systems the object is stationary and the x-ray source and detector move relative to the object—see Fig. 1.

The basic principles of x-ray laminography were described in [3] as quoted in the following paragraph:

The ability of the laminography machine to focus on specific slices in an assembly is achieved by using an x-ray source and detector that rotate in synchronized motion, 180° out of phase with one another, while the target being imaged remains stationary (Fig. 1). Images are collected continuously throughout the rotation. All of the images that are obtained for an arbitrary number of revolutions are averaged together into a final image. This causes object features that are in the focal plane to be prominent in the final image; object features that are out of the focal plane are blurred out of the image by the averaging, so these features appear only faintly. By looking at a series of laminograms of neighboring planes, it is possible to get a rough idea of the 3-D layout of layered circuits.

# C. Digital Laminography

A description was given in [4] of digital laminography, in which discrete projections were digitally stored. The analysis of the digital data enabled the extraction of images for many focal

Fig. 1. Laminography with orbiting x-ray and detector.

planes simultaneously. In addition the mathematical algorithms developed for multilayer tomosynthesis (i.e., CAT-scan) were adapted to sharpen the images.

Reference [5] described a methodology developed in 1994 to use scanned-beam x-ray laminography for the automated inspection of BGA solder joints. A set of focal planes was established in the region of the solder joints between the BGA and the PCB. The background grey-level due to the blurring of features outside the focal plane was assumed constant, and subtracted from the delta grey-level due to the solder in the focal plane. An algorithm was developed in which various soldering defects were identified from the resultant digitised images.

Much work has been done on the development of algorithms for the separation of images of layers. An algorithm was used in [6] in which the *a priori* knowledge of the joint shape and related physical principles enabled a more accurate 3-D rendering of the solder joint. An algorithm was presented in [7] that was particularly suited for separation of distinctly different layers as in PCBs or

Algorithms for reconstruction from an incomplete dataset are commonly used in medical tomography. Their application to digital laminography was justified [8] where it was shown that data from laminography could be processed as if they were taken from a tomography scan with limited access (i.e., incomplete rotation). In this method, the object was moved in a straight line across the x-ray beam, rather than in an orbit around it. Its use for surface mount and BGA devices was presented in that paper; furthermore, in [9] its applicability to PCBs and BGA substrates was discussed.

In medical tomography the dimensions of the detail within the object are of the order of tens of millimeters; however for examination of BGAs the dimensions of the detail are in tens of  $\mu$ m. An example was given in [10] of cross-sections of solder balls, extracted at layer spacings of 200 and 100  $\mu$ m. This resolution would be just sufficient to obtain separation of layers in a multilayer BGA substrate, but would not be capable of separating layers in a built-up substrate.

Recent developments in laminography equipment and software [11] have permitted layer separations by  $10 \mu m$  divisions. The equipment used in that report was a SkyScan 1080 Digital Microlaminograph. Several examples were presented including

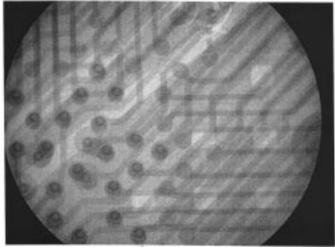

Fig. 2. Two-dimensional x-ray image of substrate with built-up layers.

a set of images showing slices across flip-chip bumps at 10  $\mu\mathrm{m}$  intervals.

#### II. THE PRESENT FAILURE ANALYSES

The use of an x-ray beam of 5 to 10  $\mu$ m focal spot size allows two capabilities:

- a) in-plane resolution of structural detail to this size;

- b) slicing of the object under study into a set of planes each of 5 to 10  $\mu$ m thickness.

This combination of fine resolution in the projected plane plus the capability of identifying the location of a feature to a particular plane of  $10~\mu m$  thickness has allowed failure analysis to be carried out in BGA structures without having to conduct DPA.

This present study used a similar machine to that in [11]. Three analyses are described in the remainder of this report. The first is the examination of individual images of copper trace patterns at 50  $\mu$ m layer spacing in a built-up substrate of a plastic BGA (PBGA); the second is the detection of gold-wire short circuits at the substrate level in a multichip low-profile fine-pitch BGA (LFBGA), and the third is the multidirectional imaging of solder balls of an LFBGA mounted on a PCB. In each case findings were made which would not have been possible with 2-D x-ray or other nondestructive technique.

#### A. Built-Up Layers in PBGA Substrate

A multichip product manufactured in 388 ball PBGA was found to have an unacceptable level of rejects after burn-in. A defect in the substrate was suspected, and as a result samples of the device were examined by 2-D x-ray (Fig. 2).

In this image there are six overlying layers. The two layers with wide traces are the layers associated with the original BT substrate. The other four layers have narrow traces, and were deposited in a built-up substrate process. One layer could not be distinguished from another in this 2-D x-ray image and so it was not possible to determine if there was a defect in any trace.BGA substrates.

Sample units were examined with the microlaminograph. A depth of 400  $\mu$ m thick incorporating the level of the built-up layers was examined. Four of the fifty images taken from this

Fig. 3. Microlaminograph images of the four built-up copper layers in the region of interest in a multichip substrate.

TABLE I LOCATION AND FUNCTION OF B-U-S LAYERS

| Layer | Height | Function                             |

|-------|--------|--------------------------------------|

| 1     | 1.177  | South West feed to inner row of vias |

| 2     | 1.224  | South West feed to outer row of vias |

| 3     | 1.270  | Links outer vias to bumps            |

| 4     | 1.324  | South West feed directly to bumps    |

analysis are shown in Fig. 3. Each one corresponds to a copper layer in the built-up portion of the substrate.

The thickness step size for this analysis was 8.3  $\mu$ m, with six to seven steps from one copper layer to the next; the copper layers were 25  $\mu$ m thick, with 25  $\mu$ m of solder resist between each, making them 50  $\mu$ m center to center. The area encompassed by the image was 4.0 mm diameter. Table I below shows the thickness increment from one copper layer to the next. The height was measured from an arbitrary datum beneath the substrate.

It was concluded from this examination that the source of the failures did not lie in the built-up copper layers of the substrate. The capability of the microlaminograph to discriminate between materials in closely spaced layers was the essential factor in enabling this conclusion to be drawn in the failure analysis of this complex product.

## B. Short-Circuits of Wire-Bonds to Substrate

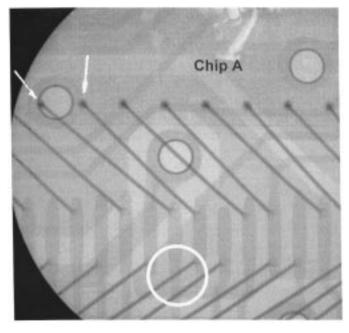

A batch of product in a 2-chip LFBGA was found to have a high level of rejects at electrical test. The yield analysis showed

Fig. 4. Two-dimensional x-ray of the region close to the short-circuit.

that most failing devices had a short circuit in one or two particular traces. The devices were examined in 2-D x-ray but nothing abnormal was seen in the bond-wire pattern.

A 2-D x-ray is shown in Fig. 4. The short circuit was detected between the two arrowed wires. The actual location of the defect is circled in white. It is a short-circuit between the wire and the tip of the bonding finger of the neighboring wire.

It was also apparent from this x-ray that the two layers of copper in the substrate were normal. It was concluded that the short circuit lay in the die or else was of a nature that was not detectable by 2-D x-ray. As several samples of this reject were available, DPA was started.

Moulding compound about 0.2 mm thick was removed from the top of some devices. This also removed the top of each wire-bond loop. The exposed wire sections were still connected either to the die or to the substrate. By electrical probing it was verified that there was not a short-circuit on the die. It was also verified that the short circuit lay between the substrate ends of two neighboring wires identified with white arrows.

Devices were examined in the microlaminograph in order to determine the location of the short circuit. In particular the routing of the short-circuit traces was examined, and nothing abnormal was found. Attention was then focussed on the routing of the related wires. A potential short-circuit was identified in the plane of the solder resist. It is visible in the circled regions in Figs. 5 and 6.

A microlaminograph image from the plane of the solder resist is shown in Fig. 5. The image location is 20  $\mu$ m higher than the plane of the copper. The device was slightly inclined in the laminograph, bringing the copper layer closer to the image plane in the upper right hand side of the image.

The image is binary rather than greyscale, in order to enhance the contrast between metal and nonmetal regions in this plane. The electroplated bonding fingers are generally visible, as are the vias in this region. The solder resist is about 25  $\mu$ m thick.

Fig. 5. X-ray Microlaminograph image showing short circuit.

Fig. 6. Photomicrograph of identical short-circuit after DPA.

A "bridge" is visible between two neighboring bond-fingers; it is highlighted with a circle in the image. These are the two bond-fingers containing the wires which had exhibited the short-circuit.

Some units were mechanically decapped from the die side by the technique described in [2]. Fig. 6 shows an optical photomicrograph of the device after DPA to expose the plane of the solder resist. The remainder of the gold wire which forms the second bond of a chip-to-substrate wirebond is highlighted by the circle. It is evident from the photograph that it made contact and caused a short-circuit with the neighboring bond-finger.

The x-ray microlaminograph and the optical photomicrograph are quite similar in the content of the images. The x-ray image closely matched the photograph of the solder resist surface after it had been exposed in DPA. This demonstrates how effective the microlaminography equipment is at discriminating

Fig. 7. Two-dimensional x-ray showing voids in solder balls.

between layers which have very little separation between them. The fine resolution of the equipment separated the closely spaced layers. The imaging software was capable of ignoring even strong data from a layer only 20  $\mu$ m away from the focal plane. The result is an x-ray image of the solder resist that is substantially free of copper traces.

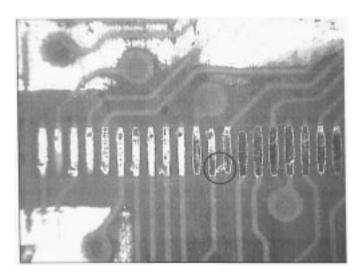

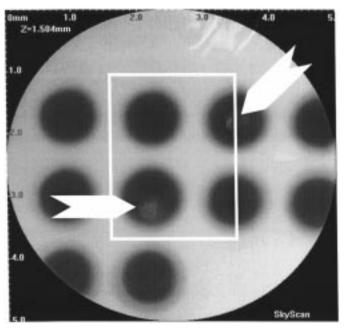

# C. Three-Dimensional Reconstruction of Solder Balls

Voids in BGA solder balls are commonly observed when using 2-D x-ray. A 2-D x-ray image through a BGA device is shown in Fig. 7. Four solder balls are highlighted by a white rectangle. Voids exist in two of these balls, marked with white arrows. However it is not possible to determine if the voids are at the interface between the substrate and the ball or at the interface between the ball and the PCB, or internal to the ball. A small void at either of the interface locations can give rise to failure of the solder joint due to absence of solder material at a critical interface, whereas a small void internal to the ball is less likely to be a reliability hazard.

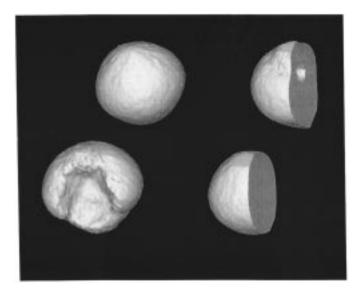

Solder has a high absorbency value for x-rays. As a result, objects composed of solder can be isolated by 3-D x-ray imaging software and presented independently of the remainder of a laminograph slice. These slices can be assembled to form a solid representation of the solder objects. It is then possible to select particular objects in the resultant data-set and to exclude the remainder. This allows the objects of interest to be viewed from any angle without obstruction of view by other objects in the line of sight.

This method has been used to isolate the 3-D reconstructions of the four individual solder balls marked in Fig. 7 by the white rectangle. It has allowed their images to be viewed from all desired angles. Defects in the balls were examined fully and conclusions drawn about their reliability. Fig. 8 illustrates the benefit of being able to de-select neighboring balls and obtain an unobstructed view of the balls of interest.

Fig. 8. Reconstruction of the same four solder balls as in Fig. 7.

The 3-D x-ray microlaminograph has the capability to determine the size and location of voids within a solder ball. The solder balls are 0.5 mm diameter. The array pitch is 0.8 mm. The voids can be seen quite clearly in the two defective balls.

Firstly there is a large external void in the near left-hand ball. This is close to the interface with the package substrate. It is about 0.3 mm across. It is a reliability hazard. The rear right-hand ball has a small void, approximately 50  $\mu$ m in diameter, and away from the surface of the ball. This is less likely to be a reliability hazard. The facility for viewing the void without obstruction from neighboring balls allowed judgement to be made about its shape and location that is not possible with 2-D x-ray.

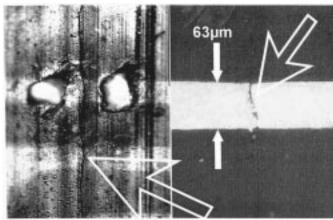

#### III. LIMITATIONS OF THE TECHNOLOGY

An attempt was made to determine the resolution limits of the equipment. PBGA assemblies were subjected to excessive Temperature Cycling at -65 to  $+150\,^{\circ}\text{C}$ . As expected, open circuits were detected, and the affected traces were identified by examination of the substrate layout plots. The devices were then examined in the 3-D x-ray microlaminograph. Despite detailed examination no evidence of the open circuit was found. These traces are approximately 25  $\mu$ m thick. The same devices were also examined in 2-D x-ray and again the cracks were not detected.

Several devices were decapped by grinding away the moulding compound and silicon to expose the solder resist over the traces. Cracks in a few traces were visually identified under an optical microscope. Openings were made in the solder resist and the existence of an open circuit was verified at each crack by electrical continuity tests between the openings.

An example of two parallel traces with cracks is shown in the left of Fig. 9; the opening in the solder resist to verify open-circuit can be seen over the upper trace. On the right is one of these traces, with the solder resist removed. The trace width was measured at 63  $\mu$ m, and the crack appears to be about 5  $\mu$ m wide for much of its length.

Fig. 9. Open circuit in trace—about  $5\mu$  m wide.

The microlaminograph had been used at maximum magnification for this investigation, and each pixel in the recovered data represented 6.4  $\mu$ m. Reinspection of the recovered images for evidence of the crack did not show anything of significance.

Accordingly it was concluded that the limits of the system had been reached, and that detail of 5  $\mu$ m or smaller could not be detected. It was also concluded that detail of less than 10  $\mu$ m would be difficult to resolve with confidence.

#### IV. CONCLUSIONS

The microlaminography equipment had been adapted successfully for the nondestructive examination of individual IC assemblies. It enabled defects in IC packages to be located and examined without recourse to destructive physical analysis.

The 3-D x-ray equipment has been used for examination of ICs to a degree of resolution better than in any previously reported work. Detailed images of four individual copper layers each 25  $\mu$ m thick, and each separated by 25  $\mu$ m of solder resist were successfully created.

A wire-to-bondfinger short was identified in the plane of the solder resist, and was successfully distinguished from the copper layer 25  $\mu$ m below. Attempts to identify this by 2-D fine beam x-ray had not been successful.

Surface and internal defects were identified and distinguished in solder balls inboard in a ball grid array that was already soldered to a PCB. 2-D x-ray could find the defects, but could not distinguish between internal and external defects in solder balls. Nor was access possible to visually inspect these balls to determine the location of the defects.

The limitations of the system were determined. Cracks in copper traces, averaging 5  $\mu$ m wide were not detected, either in 3-D or 2-D x-ray. It was concluded that there would not be confidence in resolving detail of less than 10  $\mu$ m.

#### ACKNOWLEDGMENT

The authors would like to thank K. Parmentier, Package Development Laboratory, Alcatel Microelectronics, for his help in extracting some of the images used in this report, and A. Sassov and F. Luypaert, Skyscan BV, for modifying the image processing software to suit the authors' particular needs.

#### REFERENCES

- [1] T. N. Tang et al., "Detection of underfill epoxy defects in flip chip packages with the aid of SAM, parallel polishing & FIB," in Proc. 7th Int. Symp. Phys. Failure Anal. ICs, Singapore, July 1999.

- [2] T. D. Moore and J. L. Jarvis, "Failure analysis and stress simulation in small multichip BGAs," *IEEE Trans. Adv. Packag.*, vol. 24, pp. 216–223, May 2001.

- [3] S. Gondrom and S. Schropfer, "Digital computed laminography and tomosynthesis—Functional principles and industrial applications," in Proc. Int. Symp. Comput. Tomography Ind. Applicat. Image Process. Radiology, Berlin, Germany, Mar. 1999.

- [4] S. M. Rooks, B. Benhabib, and K. C. Smith, "Development of an inspection process for ball-grid-array technology using scanned-beam x-ray laminography," *IEEE Trans. Comp., Packag., Manufact. Technol. A*, vol. 18, pp. 851–861, Dec. 1995.

- [5] A. R. Kalukin and V. Sankaran, "Three-dimensional visualization of multilayered assemblies using x-ray laminography," *IEEE Trans. Comp., Packag., Manufact. Technol. A*, vol. 20, pp. 361–366, Sept. 1997

- [6] V. Sankaran, A. R. Kalukin, and R. P. Kraft, "Improvements to x-ray laminography for automated inspection of solder joints," *IEEE Trans. Comp., Packag., Manufact. Technol. C*, vol. 21, pp. 148–154, Apr. 1998.

- [7] J. An, Y.-B. Cho, and D.-G. Gweon, "A new method for image separation of overlapped images from a two-layered printed circuit board (PCB)," *Image Vis. Comput.*, vol. 15, no. 2, pp. 861–866, 1997.

- [8] S. Gondrom et al., "x-ray computed laminography: An approach of computed tomography for applications with limited access," Nucl. Eng. Design, vol. 190, pp. 141–147, 1999.

- [9] J. An, Y.-B. Cho, and D. G. Gweon, "A new approach to translational laminographic method for PCB inspection," *Circuit World*, vol. 24, no. 2, pp. 14–20, 1998.

- [10] S. T. Kang and H. S. Cho, "A projection method for reconstructing x-rays of arbitrary cross-section," NDT&E Int., vol. 32, pp. 9–20, 1999.

- [11] A. Sassov and F. Luypaert, "X-ray digital microlaminography for BGA and flip-chip inspection," in *Proc. X-Ray Microscopy AIP '99 Conf.*, vol. 507, 1999, pp. 239–244.

**Thomas D. Moore** (M'90–SM'01) received the B.E. degree in mechanical engineering and the M.I.E. degree in industrial engineering from University College Dublin, Ireland, in 1970 and 1976 respectively.

He joined Analog Devices BV, Limerick, Ireland, in 1982 after 12 years in cement plant construction, and truck and bus design. He has almost 20 years of experience in IC packaging, in manufacturing and package development. He holds patents for thermal enhancements of standard outline plastic encapsulated ICs (these are in high volume production). His

current work is in multichip IC packaging.

Mr. Moore is a Chartered Engineer and a Fellow of the Institution of Engineers of Ireland.

**Daniel Vanderstraeten** received the M.S. degree in electronics from the BME, Ghent, Belgium.

He has more than 15 years of experience in the reliability assessment of packages and assembly lines. He is currently working in the Quality and Reliability Department, Alcatel Microelectronics, and is currently responsible for the selection and characterization of new packages, package technologies, and assembly lines. He has published several papers on scanning acoustic microscopy inspection and thermal resistance measurements.

**Pia M. Forssell** has been a Laboratory Engineer, Nokia Mobile Phones, Salo, Finland, since 1999. Her main responsibilities include management and maintenance of the Technology Analysis Laboratory and general responsibility for x-ray equipment.